摘 要:討論了基于SRAM技術的可編程邏輯器件" title="可編程邏輯器件">可編程邏輯器件FPGA的編程方式,并以ALTERA公司FLEX10K系列器件為例,提出了一種利用單片機AT89C52對FPGA進行在線PPA(被動并行異步)配置的實用方法。實踐表明,用單片機對FPGA進行并行配置,具有配置時間短、準確率高、易于實現等優點,該方法可以廣泛地應用于不同領域。

關鍵詞: 單片機 PPA FPGA 配置

在當今變化的市場環境中,產品是否便于現場升級、是否便于靈活使用,已成為產品能否進入市場的關鍵因素。在這種背景下,Altera公司的基于SRAM LUT結構的FPGA器件得到了廣泛的應用。這類器件的配置數據存儲在SRAM中。由于SRAM的掉電易失性,系統每次上電時,必須重新配置數據,只有在數據配置正確的情況下系統才能正常工作。這種器件的優點是可在線重新配置ICR(In-Circuit Reconfigurability),在線配置方式" title="配置方式">配置方式一般有兩類:一是通過下載電纜由計算機直接對其進行配置;二是通過微處理器對其進行配置。前者調試時非常方便,但在應用現場是很不現實的。因此,如果系統重新上電時,系統本身具有自動加載可編程邏輯器件的編程文件,完成對可編程邏輯器件的配置,就可以省去了通過手工由下載電纜對器件進行配置的過程。這種自動加載配置對FPGA的某些應用來說是必需的,在筆者參與研制的一種干擾系統中,利用單片機AT89C52對FLEX10K系列FPGA中的EPF10K10進行在線并行配置,取得了良好的效果。

1 FPGA器件的配置方式和配置文件

1.1 FPGA器件的配置方式

ALTERA公司生產的具有ICR功能的FPGA器件有FLEX6000、FLEX10K、APEX和ACEX等系列。它們的配置方式可分為PS(被動串行" title="被動串行">被動串行)、PPS(被動并行同步)、PPA(被動并行異步)、PSA(被動串行異步)和JTAG(Joint Test Action Group)等五種方式。這五種方式都適用于單片機配置。PS方式因電路簡單,對配置時鐘的要求相對較低而被廣泛應用。相比而言,采用PPA配置的方案卻很少見到。但由于PPA配置模式為并行配置,其配置速度快,且配置時鐘由FPGA內部產生(而PS等配置模式需要外加配置時鐘),故其更有利于在線實現。本文的配置方案便是采用PPA配置方式實現的。

1.2 FPGA器件的配置文件

ALTERA的MAX+PLUS II開發工具可以生成多種配置或編譯文件,用于不同配置方法的配置系統。對于不同的目標器件,配置數據的大小不同,配置文件的大小一般由.rbf文件(即二進制文件)決定。本實例中,EPF10K10的配置文件.rbf的大小為15K。該文件包括所有的配置數據,一個字節的.rbf文件有8位配置數據。由于Altera提供的軟件工具不自動生成.rbf文件,故文件需按照下面的步驟生成:①在MAX+PLUS II編譯狀態下,選擇文件菜單中的變換SRAM目標文件命令;②在變換SRAM目標文件對話框,指定要轉換的文件并且選擇輸出文件格式為.rbf(Sequential),之后予以確定。

2 硬件電路設計

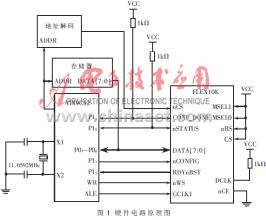

AT89C52對EPF10K10并行配置的硬件電路示意圖如圖1所示。經MAX+PLUS II編譯生成配置文件(.sof),通過格式轉換成為(.rbf)文件并存儲在圖中所示的存儲器中。當使用PPA配置方式時,需要將MSEL1和MSEL0置為高電平" title="高電平">高電平。為了不使DCLK出現不確定信號,必須將其經過1kΩ電阻上拉到Vcc。在采用PPA配置方式時,nCS和CS兩個片選信號只需用一個。因此,如果采用其中一個作為片選信號,另一個必須直接置為有效位;如果選用CS作為片選信號控制配置,nCS必須接地;如果選用nCS作為片選信號控制配置,CS必須接高電平。本實例中采用后者。nRS為讀選通輸入信號,它為低輸入時,FLEX10K將RDYnBSY信號置于DATA7引腳。當nRS不用時,必須將其置為高。nCE為FLEX10K器件的使能輸入,nCE為低時使能配置過程。當器件是單片配置時,nCE必須始終為低。由于本實例為單片配置,故將nCE直接接地。然后將EPF10K10的nCONFIG、CONF_DONE、nSTATUS、RDYnBSY分別接到AT89C52的P17、P14、P15、P13引腳上。DATA[7..0]接到AT89C52的P07~P00。nWS為寫選通輸入,由低到高跳變時鎖存DATA[7..0]引腳上的字節數據。要注意的是,nSTATUS引腳和CONF_DONE引腳是雙向漏極開路端口,在作輸出使用時,應該經過1.0kΩ的電阻上拉到Vcc。

3 軟件設計

3.1 配置原理

PPA配置方式的下載時序如圖2所示。由圖可以看出PPA模式的工作過程如下:

(1)啟動配置

在nCONFIG引腳上產生一個低脈沖,等待nSTATUS回應一個低脈沖以及CONF_DONE變低。在nCONFIG跳高后4μs,內nSTATUS也跳高,表明FPGA可以配置了。

(2)配置過程

在對FPGA進行配置時,單片機將8位的配置數據放在FPGA器件的數據端,并且給nWS一個負脈沖,在nWS的上升沿,FPGA器件將該字節配置數據鎖存;然后FPGA器件驅動RDYnBSY為低,表明它正在處理該字節信息,配置過程可以通過nCS或CS引腳暫停。當RDYnBSY為低電平時,FLEX10K器件利用其內部振蕩器(其頻率一般為10MHz)在其內部將每一個字節的配置數據串行化。當FLEX10K器件準備接收下一個配置數據時,就使RDYnBSY變高。單片機檢測該高電平信號后,送出下一個字節的數據。這一過程一直持續到全部數據配置完成。在配置過程中,系統需要進行實時監測,一旦出現錯誤,nSTATUS將被拉低,系統必須能識別出這個信號,并重新啟動配置過程。

(3)結束配置

配置數據全部正確寫入芯片內部后,器件釋放CONF_DONE,由外部將其拉高。如果單片機檢測到這個信號,則表明配置成功;否則,要對其重新配置。PPA方式時序參數如表1所示。

3.2 配置軟件設計

單片機實現配置過程的控制程序流程圖如圖3所示。

匯編程序設計如下:

nCONFIG EQU P1.7

nSTATUS EQU P1.5

RDYnBSY EQU P1.3

CONF_DONE EQU P1.4

ORG 0000H

LJMP MAIN

ORG 0030H

;對數據長度" title="數據長度">數據長度相關進行初始化,其中所要配置的數據長度放在地址為0000H和0001H中

;0000H放數據長度的低位,0001H放數據長度的高位

;從0002H開始放置的是所要配置的數據

MAIN: MOV DPTR,#0000H

MOVX A,@DPTR

MOV R3,A; R3放配置數據個數的低位

MOV DPTR,#0001H

MOVX A,@DPTR

MOV R4,A; R4放配置數據個數的高位

MOV R5,#00H ;放配置數據個數的低位

MOV R6,#00H ;放配置數據個數的高位

;以下是將數據進行配置的子程序

COFIG: MOV DPTR,#0002H

CLR P1.7

ACALL DELAY4 ;延時約為15μs

JB nSTATUS,COFIG ;檢測FPGA是否響應置低位

SETB nCONFIG ;FPGA響應置低位后,將nCONFIG置高位

STA_JUDGE: JB nSTATUS,COFIG_BEG ;等待FPGA是否響應置高位,然后準備進行配置

LJMP STA_JUDGE

COFIG_BEG: ACALL DELAY2

LJMP SEND_DATA

READY_DATA1:JNB nSTATUS,COFIG

SEND_DATA: MOVX A,@DPTR ;讀取數據

PUSH DPH

PUSH DPL

MOV DPTR,#7000H ;讀入FPGA地址

JNB P1.3,$ ;判斷RDYnBSY的狀態

MOVX @DPTR,A ;配置數據

POP DPL

POP DPH

INC DPTR ;以下實現配置個數的判斷

CLR C;

MOV A,#01H

ADD A,R5

MOV R5,A

MOV A,#00H

ADDC A,R6

MOV R6,A

MOV A,R5

CJNE A,03H,RESESH_COFIG

MOV A,R6

CJNE A,04H,RESESH_COFIG

CON_REFRESH: ACALL DELAY2 ;延時5μs,

JB P1.4,END1 ;判斷CONF_DONE的狀態,看是否配置成功

LJMP COFIG

RESESH_COFIG: LJMP READY_DATA1

;延時子程序,延時約為5μs

DELAY2: NOP

NOP

NOP

NOP

NOP

RET

;延時子程序,延時約為15μs

DELAY4: MOV R1,#08H

DJNZ R1,$

RET

END1: END

本文討論的基于單片機的FPGA并行配置方法具有線路結構簡單、開發容易、成本低的特點。與常用的串行配置方法相比,該配置方法更具有配置時間短、準確率高、易于實現等優點。雖然該配置控制電路是為配置ALTERA公司FLEX10k系列的FPGA器件而設計的,但稍加修改也適用于其它系列的FPGA器件,故其有一定的通用性。

參考文獻

1 劉曉明,王 軍,謝明欽.基于單片機的復雜可編程邏輯器件快速配置方法[J].電子技術應用,2002;28(10)9~11

2 薛鈞義,張彥斌.MCS-51/96系列單片機微型計算機及其應用[M].西安:西安交通大學出版社,1997.8

3王玉花,郭書軍,葛紉秋.FPGA器件的在線配置方法.單片機及嵌入式系統應用[J],2004,3:8~10

4 胡修林,席向清,張蘊玉.嵌入式系統在FPGA的被動串行配置方法.單片機及嵌入式系統應用[J],2004.3:21~31

5 宋萬杰,羅 豐,吳順君.CPLD技術及其應用[M]. 西安:西安電子科技大學出版社,2000