MOSFET能夠將導通電阻再降低一點那就棒了。電阻導致發熱,換而言之就是浪費電能。為何你們不能環保一點呢? – 潮州怒漢上

親愛的FAE博士:

我將飛兆半導體的FET置于高頻下工作,而開關損耗成為耗電的罪魁禍首。我不理解,為何你們不能再努力一點,使器件開關所需的柵極電荷再減低一些,從而減少耗電。為何你們不能環保一點,老是要浪費這么多電能?- 深圳心煩人上

親愛的潮州怒漢和深圳心煩人:

今天你們真幸運。咖啡師給我弄了杯非常棒的拿鐵濃咖啡,還在那層厚薄恰到好處的牛奶泡沫上畫上一個心型點綴。因此,我發誓今天不會因任何事情壞了我的心情。今天可是我的好日子哦。上下班堵車?這不是問題。行人慢騰騰過街?我不會煩躁。煩人的問題?我會笑臉相迎。

我們經常接到這樣的問題。難道還有誰比我們這群在實驗室和生產車間拼命工作,年復一年提供更好的MOSFET 的天才更不受人賞識的嗎?我們最近推出了首款采用Power56 封裝,電阻低于1 mOhm的30V N溝道MOSFET器件(FDMS7650)。你大概可以想象到在產品發布時,我們整個工程部都沉浸在狂歡之中。

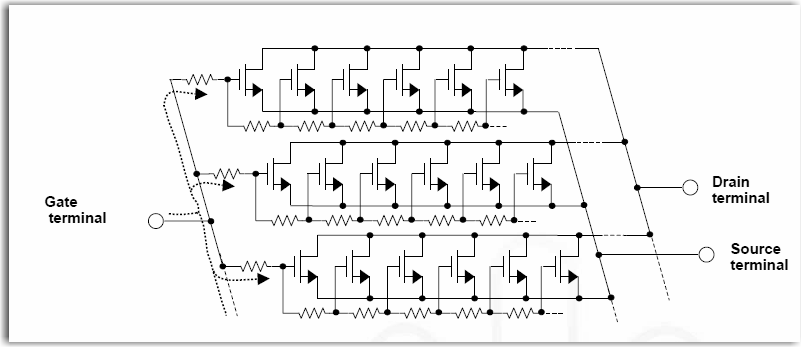

好了,讓我回答這兩位朋友的問題。你認為你買的是一個MOSFET器件,但實際上,你購買的是很多個MOSFET器件(可能數百萬,甚至數千萬),我們降低導通電阻的方法是:在裸片上填充更多的并聯晶體管。我們的品質因數是每平方厘米面積裸片的電阻值,而且我們每年都在降低這個數值。

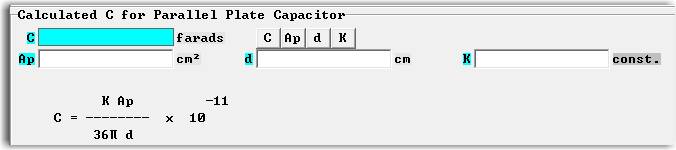

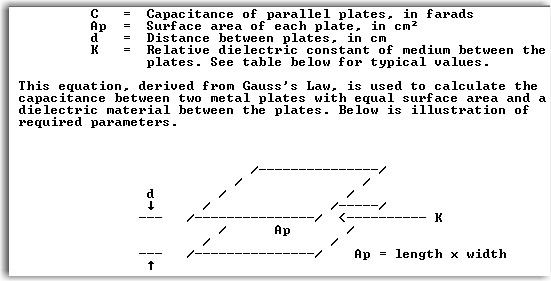

我知道你在想什么…要利用溝槽技術來構建所有這些晶體管,最大限度地增加漏極和源極表面積,同時保持低電容,從而最大限度地降低柵極電荷需求,一定是件非常困難的事情。的確是個挑戰。下面是電容的基本計算公式:

圖2:基本的電容計算方法

這個計算公式提醒我們電容隨“平板”面積增加,以及平板間距離減少而增大。這意味著,當我們通過增加并聯晶體管來降低電阻的同時,電容一般也會增加。當然,我們會盡其所能…注意介電常數K值… 如果能夠減小K值,就會對我們有利。當然如果pi值提高,對我們也有利,因此,我們在呼吁國際標準化組織將pi值提高,比如是5這一類容易記憶的數值 (這就是所謂仔細無遺的工程師幽默啊)。

我們以兩種方式在市場體現產品價值;要么使用較小的裸片,以較低的成本,實現同樣的導通電阻;要么以相同的價格實現更低的導通電阻。可是可曾有人為此來電感謝我們嗎?對,很少有人會這么樣做。

我們認識到客戶對柵極電荷的需求,并通過電荷均衡來全力控制它,使其變得更小。不過從前述兩封讀者來信所見,讓所有客戶都滿意是很難的事情,但我們在繼續嘗試。

至于環保的問題,我的回應是:我小時候曾養過一頭土耳其安哥拉貓,它后來死于環境污染。你想,我會不關注環保嗎?好吧,如果不介意的話,我還是回去品嘗可口芬芳的拿鐵咖啡了。