1 引 言

校正器作為自適應光學系統的核心部件,在很大程度上決定著自適應技術發展的方向。目前在自適應光學系統使用較多的是變形鏡校正器。

隨著自適應技術在眼底觀測方向的使用,傳統變形鏡校正器顯露出其固有的缺點,由于受校正單元少的限制,變形鏡校正器很難對存在高階像差的眼底成像。因此,校正單元多的液晶校正器開始在眼底觀測領域廣泛使用。與玻璃基板液晶顯示器相比,采用硅基板的液晶顯示器(LCOS)由于具有尺寸小、分辨率高、光效利用率高等優點,成為目前的最佳選擇。作為LCOS驅動電路的核心———為液晶模塊(LCM)提供顯示數據和時序信號的LCOS控制器通常都是由專用集成電路(ASIC)組成。在實際工程應用中,需要各種分辨率的LCOS,由于每一種LCOS都需要專門的顯示控制器,因此LCOS的設計和使用都比較繁瑣。

本設計采用現場可編程門陣列(FPGA)器件來代替ASIC,利用可編程片上系統(SOPC)實現通用LCOS顯示控制器的設計。在使用中只需通過對軟件參數進行修改,即可完成對不同分辨率 LCOS的控制。由于液晶自適應系統需要傳輸的數據量很大,所以為了保證系統的實時性,采用USB2.0協議進行數據傳輸。本文使用了NXP公司的PDIUSBD12的USB芯片、ALTERA公司的EP1C6Q240C8器件,采用C++語言設計了USB驅動程序和固件程序,利用VHDL硬件描述語言設計了通用LCOS控制器并在實際應用中通過測試,基本上實現了通用LCOS控制器的預期目標。

2 系統原理

LCOS的顯示采用逐行掃描方式,即當一行被選通以后,這一行中的各列信號同時加到列上,并維持一個掃描行的時間,當這一時間結束后選通下一行,各列電極施加下一行的顯示電壓。

目前普通的液晶控制器都是由存儲器和控制器組成,由一塊MCU 接收上位機發送過來的顯示數據,并由該MCU分配存儲地址,生成時序信號,把數據存入存儲器中,而后由液晶顯示模塊讀取存儲器中的數據。存儲器的存取速度較慢,在讀寫大批量數據時很費時,很難匹配LCOS的響應速度,并且當更換不同分辨率的LCOS顯示模塊后還需要有新的控制器,存在成本太高且過程煩瑣的缺點。

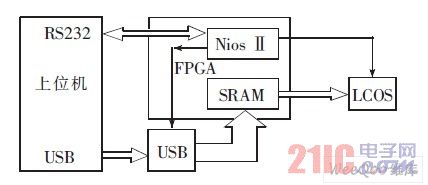

有鑒于此,本文提出了基于SOPC 設計LCOS控制器的思路,即在FPGA 內構建一個NIOSⅡ軟核處理器和SRAM 存儲器,把SRAM映射到LCOS顯示模塊的數據緩沖區,將NIOSⅡ與PDIUSBD12以DMA 的方式連接,將NIOSⅡ與上位機以串口的方式連接,通過設置LCOS參數和存儲器規模參數在內的各種參數,適應不同分辨率的LCOS;通過DMA方式節省傳輸時間;通過把SRAM 映射到顯示數據緩沖區節省存儲器的存取時間。如圖1所示。

LCOS系統原理圖

圖1 LCOS系統原理圖。

3 系統設計

3.1 系統引腳信號時序分析

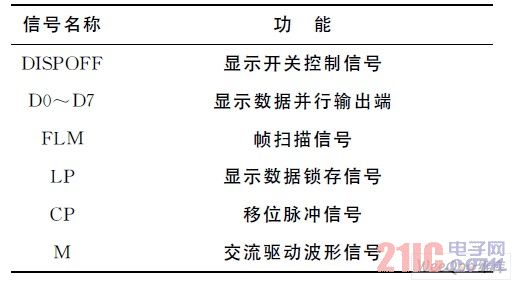

一般來說,LCM 引腳都具有如表1所示的功能描述。

表1 LCM 引腳信號功能

LCM 引腳信號功能

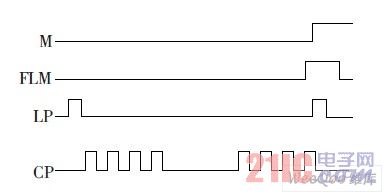

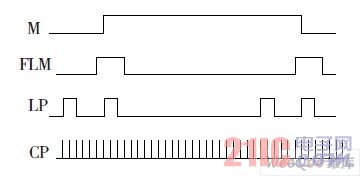

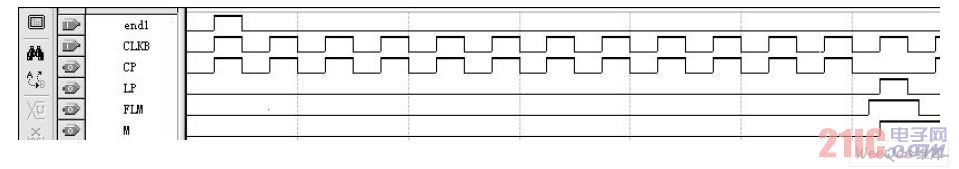

每個CP移位脈沖信號都是通過一系列CP脈沖,把完整的一行顯示數據(D0~D7)存入移位寄存器中。移位寄存器與鎖存器并口相接,當完整的一行顯示數據被存入移位寄存器后,在鎖存信號LP的作用下,該行數據被鎖存到鎖存器內,并輸出給列電極。因此LP的周期應為一個行周期。當一幀圖像的最后一行顯示數據存入移位寄存器后,FLM 幀掃描信號變成高電平,其脈寬維持超過一個LP脈寬。因此FLM 的周期應為一幀圖像的時間,即各行LP的周期和。M 是液晶顯示模塊的交流驅動信號,每一幀時間改變一次波形的極性,可以防止液晶顯示的單方向扭曲變形。更為詳細的引腳信號時序關系如圖2和圖3所示。

引腳信號的時序關系1

圖2 引腳信號的時序關系1。

圖3 引腳信號的時序關系2。

3.2 參數確定

在設計通用分辨率的LCOS控制器之前,先要確定某些參數。這些參數包括LCOS的分辨率m×n,LCOS的灰度級2u(一般情況下LCOS的灰度為256),LCOS顯示器的刷新頻率a Hz,信號CP的頻率b MHz等。這些參數由上位機通過串口發送到NIOSⅡ處理器中。根據這些參數,由NIOSⅡ計算得到如下關系:每一幀的周期為 103/a(ms);每一行的周期為106a-1 n-1(us);將一行顯示數據寫入寄存器的時間為m/b (μs);每一行的空時間[106a-1n-1]-[m/b]us),這一項應當不小于0。依據計算后的數據和圖2、圖3所示的信號關系,使用定時器和脈寬調制器(PWM)生成LCOS的邏輯控制信號。同樣在NIOSⅡ中還要完成SRAM 內存的設計,內存的實現是依靠FPGA 中的邏輯門陣列來實現的。設計所遵循的原則是SRAM 的容量能至少裝下完整的2幀數據,即2m×n×2u,一幀數據存儲區用于當前顯示,另一幀數據存儲區同時接收下一幀要顯示的數據,這樣的策略雖然耗費了大量的邏輯門數量,卻可以使低速的存儲器和高速的LCOS顯示器相匹配,同時更好地發揮USB的速度優勢。

4 實例設計

在實際應用中,以256×256分辨率、256灰度級的LCOS為例來設計LCOS控制器。

首先根據已有的LCOS計算各種參數。對于256×256的LCOS,其刷新頻率為200Hz,時鐘信號CLKB的頻率為20MHz。因此,每一幀的周期為5ms,每一行的周期為19.53μs(相當于391個CLKB時鐘周期時間),將一行顯示數據寫入寄存器的時間為12.8μs(相當于256個CLKB時鐘周期時間),每一行的空時間為6.73μs(相當于135個CLKB時鐘周期時間)。如果設計時發現每一行的空時間小于0,則要提高時鐘信號CLKB的頻率。

接下來是設計SRAM 存儲器,SRAM 容量的設計原則是能裝下完整的2幀數據,即2×256×256×256就能裝下完整的2幀數據,但為了便于CPU還可以完成其他計算的需要,內存的設計要比2幀數據大一些,這里取3幀數據容量,同時設定固定的區域為顯示緩沖區。

將USB的數據輸入緩沖區同樣設在該顯示緩沖區域,這樣通過USB端口輸入的待顯示數據直接存儲在顯示緩沖區域。

然后是將外部的LCOS顯示器的數據輸入端口作為NIOSⅡ處理器的I/O 映射地址,通過DMA處理,使NIOSⅡ內存的顯示緩沖區以DMA的方式通過AHB總線與LCOS顯示器的數據輸入端口直接輸入。使用DMA和總線的好處是既簡便快速,傳輸又很穩定。

在QuartusⅡ6.0環境下對NIOSⅡ控制器進行功能仿真測試,仿真的波形如圖4所示。該控制器的時序信號符合設計要求。完成功能仿真后,經過綜合生成門級網表,下載到ALTERA公司Cyclone系列EP1C6Q240C8器件中。

NIOSⅡ控制器的功能仿真波形

圖4 NIOSⅡ控制器的功能仿真波形。

5 結 論

利用SOPC和USB設計了一種LCOS通用控制器。通常LCOS的價格較高且不能通用,利用本文的方法可以最大限度地降低材料成本和設計成本,并且可以根據應用的需要,通過發送不同的參數適應于不同的LCOS顯示器。由于采用軟核處理器,系統的穩定性稍差一些,并且PDIUSBD12的速度僅為12MB/s。為了提高系統的穩定性,可以使用ARM9 處理器;為了發揮USB2.0 的全速480 MB/s,可以使用新一代CH375USB控制器。這樣就可以使LCOS通用控制器擁有更優秀的性能。