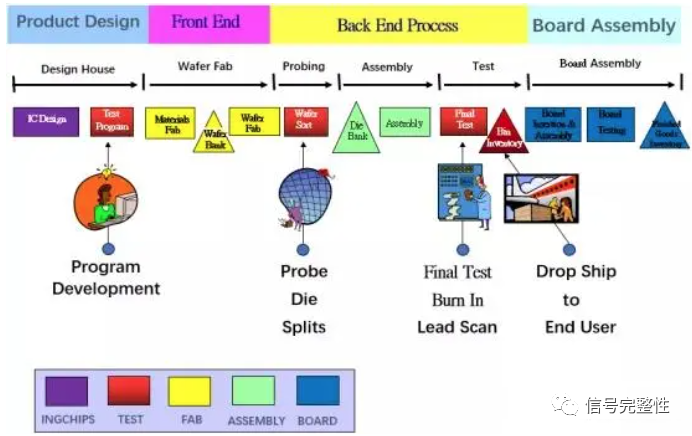

半導體生產流程由晶圓制造,晶圓測試,芯片封裝和封裝后測試組成。而測試環節主要集中在CP(chip probing)、FT(Final Test)和WAT(Wafer Acceptance Test)三個環節。

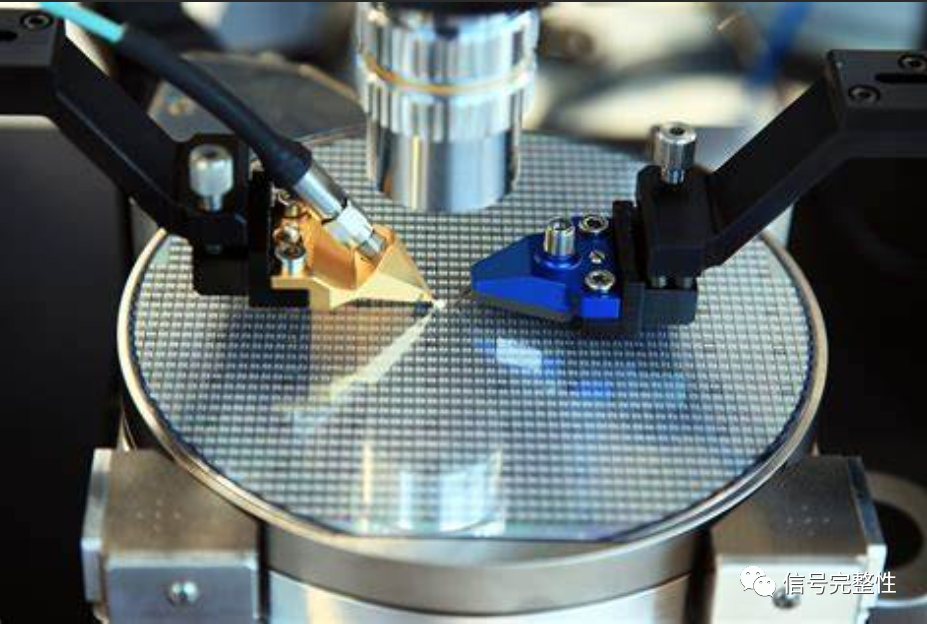

CP測試,英文全稱Circuit Probing、Chip Probing,也稱為晶圓測試,測試對象是針對整片wafer中的每一個Die,目的是確保整片wafer中的每一個Die都能基本滿足器件的特征或者設計規格書,通常包括電壓、電流、時序和功能的驗證,如vt(閾值電壓),Rdson(導通電阻),BVdss(源漏擊穿電壓),Igss(柵源漏電流),Idss(漏源漏電流)等,可以用來檢測fab廠制造的工藝水平。可以更直接的知道Wafer的良率。

CP的難點是如何在最短的時間內挑出壞的die,修補die。

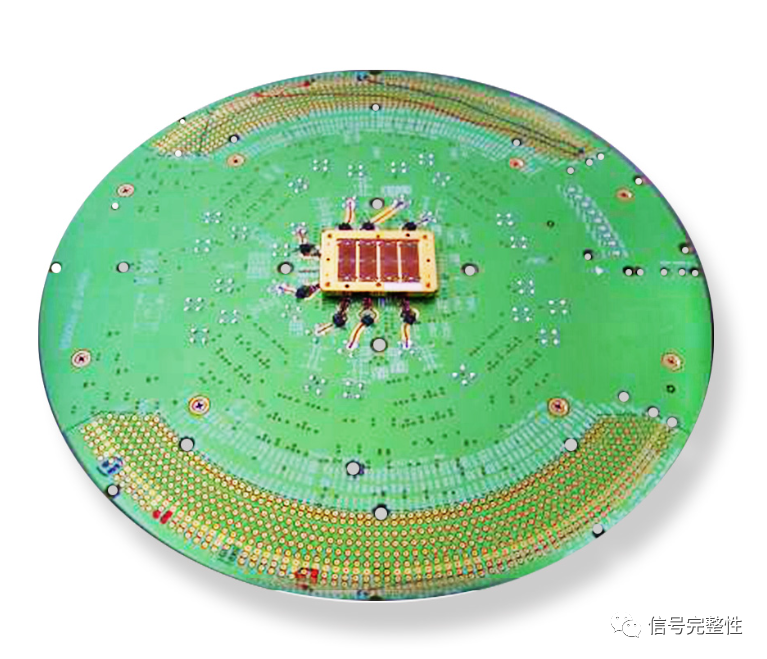

常用到的設備有測試機(Tester) 、探針臺(Prober) 以及測試機與探針卡之間的接口(Mechanical lnterface)。一般測試機臺的電壓和功率不會很高。

FT測試,英文全稱Final Test,是芯片出廠前的最后一道攔截。測試對象是針對封裝好的chip,CP測試之后會進行封裝,封裝之后進行FT測試,也叫“終測”。可以用來檢測封裝廠的工藝水平。FT是把壞的chip挑出來;檢驗封裝的良率。測試完這道工序就直接賣去做應用了。

FT測試一般分為兩個步驟:1)自動測試設備 (ATE) 2) 系統級別測試SLT) --2是必須項,1一般小公司可能用不起,ATE試一般只需要幾秒鐘;SLT一般需要幾個小時,邏輯比較簡單。

FT的難點是如何在最短的時間內保證出廠的Unit能夠完成全部的功能。FT需要tester (ATE) + handler + socket。

CP對整片Wafer的每個Die來測試,而FT則對封裝好的Chip來測試。CP Pass 才會去封裝。然后FT,確保封裝后也Pass。

WAT是Wafer Acceptance Test,對專門的測試圖形(test key)的測試,通過電參數來監控各步工藝是否正常和穩定;WAT(Wafer Acceptance Test)測試,也叫PCM(Process Control Monitoring),對Wafer 劃片槽(Scribe Line)測試鍵(Test Key)的測試,通過電性參數來監控各步工藝是否正常和穩定。

WAT測試有問題,超過SPEC,一般對應Fab各個Module制程工藝或者機臺Shift,例如Litho OVL異常,ETCH CD 偏小,PVD TK偏大等等。WAT有嚴重問題的Wafer會直接報廢。

對于測試項來說,有些測試項在CP時會進行測試,在FT時就不用再次進行測試了,節省了FT測試時間;但是有些測試項必須在FT時才進行測試(不同的設計公司會有不同的要求)。

一般來說,CP測試的項目比較多,比較全;FT測的項目比較少,但都是關鍵項目,條件嚴格。但也有很多公司只做FT不做CP(如果FT和封裝yield高的話,CP就失去意義了)。

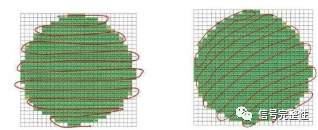

在測試方面,CP比較難的是探針卡的制作,并行測試的干擾問題。FT相對來說簡單一點。還有一點,memory的CP測試會更難,因為要做redundancy analysis,寫程序很麻煩。

WAT測試有問題,超過SPEC,一般對應Fab各個Module制程工藝或者機臺Shift,例如Litho OVL異常,ETCH CD 偏小,PVD TK偏大等等。WAT有嚴重問題的Wafer會直接報廢。

對于測試項來說,有些測試項在CP時會進行測試,在FT時就不用再次進行測試了,節省了FT測試時間;但是有些測試項必須在FT時才進行測試(不同的設計公司會有不同的要求)。

一般來說,CP測試的項目比較多,比較全;FT測的項目比較少,但都是關鍵項目,條件嚴格。但也有很多公司只做FT不做CP(如果FT和封裝yield高的話,CP就失去意義了)。

在測試方面,CP比較難的是探針卡的制作,并行測試的干擾問題。FT相對來說簡單一點。還有一點,memory的CP測試會更難,因為要做redundancy analysis,寫程序很麻煩。

關于3溫測試:這是一種特殊的測試方法,它要求在三個不同的溫度下對產品進行測試,通常是常溫(25℃左右)、高溫(如60℃或70℃)和低溫(如-20℃或-40℃)。這種測試的目的是為了檢查產品在不同溫度下的性能和可靠性,以確保產品能在不同環境下正常工作。