1 引言

待機是指產(chǎn)品已連接到電源上,但處于未運行在其主要功能時的狀態(tài)。待機的目的就是要降低電源在空載或輕載時的損耗。隨著電器和網(wǎng)絡產(chǎn)品的普及,電子產(chǎn)品待機狀態(tài)下的耗電量越來越引起國際節(jié)能,環(huán)保組織和有關(guān)國家的重視。待機能耗不僅浪費電能,而且也制造巨大的環(huán)保壓力。我們知道開關(guān)損耗與電源的工作頻率成正比,因此,可以設(shè)法在電源輸出功率變小乃至于進入待機狀態(tài)時,使其工作頻率降低。這可以通過許多控制功能芯片" title="芯片">芯片來實現(xiàn),例如集成芯片L5991等。目前,很多PWM" title="PWM">PWM芯片還不具有變頻的待機功能" title="待機功能">待機功能,因而,我們可以借鑒L5991芯片的這個功能電路來實現(xiàn)其他PWM芯片的待機功能。

2 L5991芯片的待機功能電路介紹

L5991芯片,是由BCD60II技術(shù)發(fā)展而來的,設(shè)計目的是用一個固定頻率的電流模式控制,實現(xiàn)離線式DC/DC電源應用。L5991是一個標準電流型PWM控制器,該控制器具有可編程軟啟動,輸出/輸入同步,閉鎖(用于過壓保護和電源管理),精確的極限占空比控制,脈沖電流限制,用軟啟動來進行過流保護,和當空載或輕載時使振蕩器頻率降低的待機功能等優(yōu)點。

圖1是該芯片待機功能的基本內(nèi)部電路。管腳2外接兩個電阻(RA和RB)和一個電容(CT),照圖1中連接,是用來分別設(shè)置振蕩器正常運行的工作頻率(fosc)和待機模式的工作頻率(fsb)。實際上,只要待機信號是高電平,該管腳能通過一個N溝道FET內(nèi)部連于參考電壓Vref,所以,定時電容CT通過RA和RB放電。當待機信號變低,N溝道FET就關(guān)閉且該管腳懸空,CT只通過RA放電,這樣振蕩器頻率就會變低。VCT在正常運行中由Vref通過RA和RB控制,而在待機時通過RA來進行調(diào)控。當CT上的電壓達到3V時,電容會快速地內(nèi)部放電。當電壓降到1V時,它開始再次充電。

圖1 L5991芯片的待機功能基本電路

正常運行中RT將等于RA//RB,其頻率公式為

fosc≌ (1)

而在待機時RT=RA,其頻率公式為:

fSB≌ (2)

式中:KT=

L5991通過對與負載相聯(lián)系的反饋電壓進行檢測,在負載降低到一個定義值(由電路中的元器件參數(shù)來控制)時自動降低振蕩器頻率,而當負載增加并超過第二個極限值時恢復其正常工作頻率。這樣,由L5991控制工作頻率的系統(tǒng),就可以依靠其待機功能來實現(xiàn)系統(tǒng)待機和工作時的頻率轉(zhuǎn)換。當系統(tǒng)待機時,頻率降低,可以通過對電路參數(shù)的設(shè)置使待機頻率變得很低,從而降低了開關(guān)損耗。

L5991作為一個電流型控制器,其誤差放大器的輸出電壓Vcomp,除偏移量外,是跟主電流峰值成比例的。所以,可以通過監(jiān)控Vcomp來推測電源的負載情況。

假如,由于負載減小使得主電流峰值降低,且Vcomp降低到一個固定極限(VT1)時,振蕩器頻率將被設(shè)置到一個較低的數(shù)值上(fsb)。假如,主電流峰值增加且Vcomp超過VT2時,振蕩器頻率將重置在正常值上(fosc)。頻率的變化引起Vcomp的變化,并且由于能量平衡原因而方向相反,因而,提供一個恰當?shù)臏蟊憧梢苑乐拐袷幤黝l率在fsb與fosc之間變動。

3 反激式開關(guān)電源" title="開關(guān)電源">開關(guān)電源待機功能的實現(xiàn)

根據(jù)上述L5991芯片的待機原理,我們可以試想,在UC3842構(gòu)成的反激式開關(guān)電源的基礎(chǔ)上加入待機功能。通過對與負載相聯(lián)系的反饋電壓進行檢測,利用芯片內(nèi)部的誤差放大器的輸出值,對頻率進行改變。

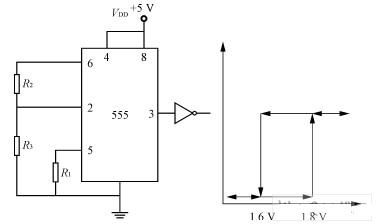

UC3842芯片的管腳1為誤差放大器輸出,圖2為芯片待機功能的基本電路。

圖2 芯片待機功能的基本電路

該電路的主要原理是:檢測反饋電壓經(jīng)誤差放大器后的輸出值,通過一個遲滯比較器(施密特觸發(fā)器),驅(qū)動開關(guān)管的開通或者關(guān)斷,來實現(xiàn)RT的改變,從而改變電源的振蕩頻率。

我們可以看到,電源處于何種工作狀態(tài)(正常工作或是待機),取決于遲滯比較器的閾值的設(shè)定,而該閾值取決于電源待機和正常工作時的誤差放大器的輸出值。

在實際設(shè)計的電路中,電源電路空載時,輸出約為1.6V,而非輕載時為1.8V以上,因而,我們根據(jù)這個值來設(shè)定遲滯比較器的閾值。遲滯比較器由555芯片加上外圍的電阻構(gòu)成,該比較器的電路圖如圖3所示。

圖3 遲滯比較器電路

圖3中,555芯片的基準電源VDD為+5V,由UC3842的腳8輸出基準電壓給定。遲滯比較器的上下閾值計算如下:

VTH=VDD (3)

VTL= (4)

根據(jù)以上確定的閾值,確定各個電阻的阻值。

電源電路負載變化時,根據(jù)遲滯比較器的閾值,電源工作在相應的頻率。

4 試驗結(jié)果

根據(jù)以上原理搭構(gòu)了由UC3842芯片控制的單端反激式開關(guān)電源電路[1][2][3],并加入了待機電路,其中取CT=4700μF,RA=RB=20kΩ,驗證了以上原理。

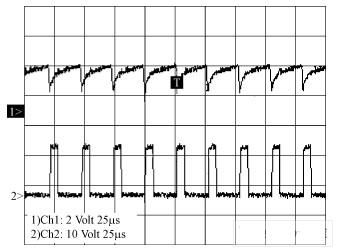

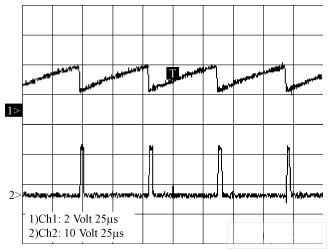

圖4為空載切換成帶5W負載時的頻率變化,頻率由20kHz變成40kHz,而當切換回空載時,頻率則由40kHz變回了20kHz,如圖5所示。

圖4 空載切換成帶負載時頻率變換

圖5 負載切換成空載時的頻率變換

圖6及圖7給出了正常工作狀態(tài)和待機工作狀態(tài)下的電源電路的振蕩脈沖和功率MOSFET器件的驅(qū)動信號波形。從圖中可以清楚的看出電源的工作頻率。

圖6 正常工作時的振蕩脈沖和驅(qū)動波形

圖7 待機工作狀態(tài)下的振蕩脈沖和驅(qū)動波形

5 結(jié)語

由UC3842構(gòu)成的開關(guān)電源,完全可以加入待機功能電路來實現(xiàn)待機功能,在空載的時候降低開關(guān)頻率,有效地減少開關(guān)損耗。并且,完全可以在其他PWM芯片上也加入類似的檢測控制電路來實現(xiàn)待機功能。